|

|

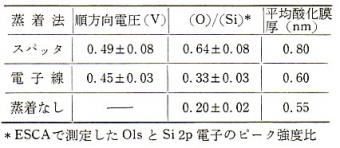

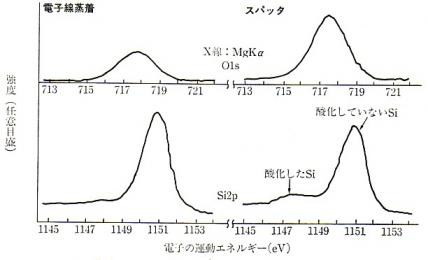

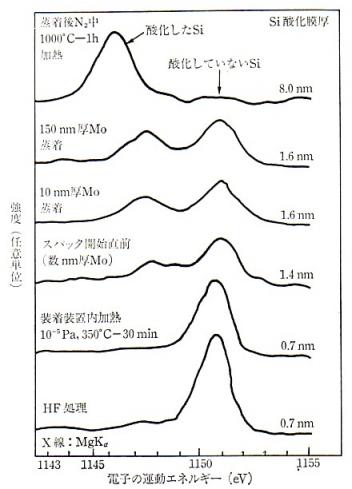

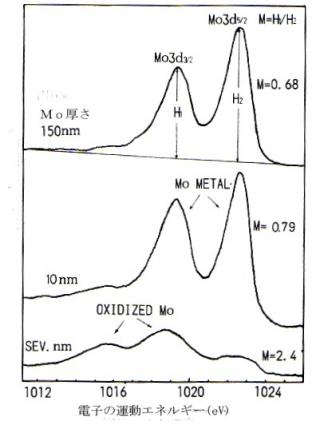

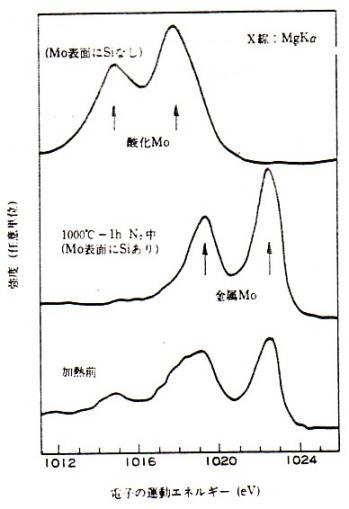

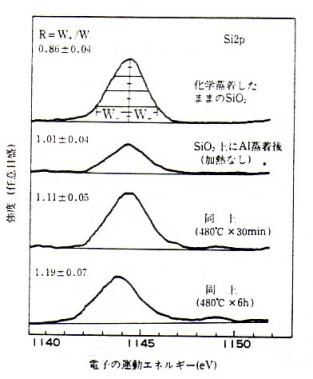

私の問題解決の考え方 第6章第6章 やる気が出てきた!-「会社の」研究が「私の」研究にー 会社に入ってから私に与えられた研究の初期目的は、「会社の」半導体製造技術に関するいろいろな問題(与えられる)を解決することでした。 私にとっては未経験の問題ではありましたが、研究を始めていろいろやっているうちに、仕事に少しずつ馴れ、その内容も少しずつ分かってきました。 その頃(1970年代)の技術開発では、 1)多くの場合、試行錯誤的(失敗したら他のことをやる繰り返し)に問題を解決しようとしてきた。 2)このとき、試行を、事実より、あてずっぽうだったり、想像をもとに、行なうことが多かった。そして、やったことの良し悪しをきちんと判断していなかった。 3)問題の内容としては,材料の表面(界面)に関係するものが多かった。 が明らかになりました。 これらのことから、私としては、 1)これまでの試行錯誤法をチェック機能付きにする。それも全工程の途中段階でチェックしたい。 2)会社の問題の多くのものでは、材料表面(界面)状態の把握が重要であると判断した。 3)そのための、表面(界面)状態を評価(分析)する測定装置を手に入れる。 のように考えることにより、会社の様々な問題の解決に立ち向かっていきました。 とりあえず、会社の問題を解決しながら、表面評価装置を導入し、表面(界面)分析技術の立ち上げ(これも未経験)も同時に行ないました。そして、分析の練習の段階から、問題解決に役立てていきました。 上記装置(エスカ)は、私が苦労して手に入れて、私のところで測定できるようにしたものなので、この装置を、会社のエスカというより、「私の」エスカと考えるようになってしまいました。 そして、会社の問題についても、ほとんどのものにエスカ(X線光電子分光)を使ったので、これらの問題も次第に「私の」問題となってきたのでした。 このような展開になったのは、会社の技術開発のための必要性もありましたが、私の、表面(界面)研究への興味が大きな要因でした。 しかし、私は,そもそも、この分野の専門家であったわけではなく、研究のために使う測定装置も持っていませんでした。 この頃、偶々、私の研究に使えそうな分析装置(元わが社が開発したのに、この事業を止める決定をした)が廃棄処分になりそうだったものを只で手に入れることに成功したのでした。 その結果、この装置(エスカ)を立ち上げ、使いこなす仕事までやることになってしまいましたが、これが会社の研究を私の好きなことの方向へ向けてくれたのでした。表向きは会社の技術開発の研究なのですが、私はかなりの時間を表面、界面の研究に割いていました。 そして、「会社の」研究が少しずつ「私の」研究になっていったのです。つまり、会社から与えられたり、工場から相談されたようなこととして、問題解決を、最初は特にやりたいとは思わずに始めるのですが、とにかく調べてみると、少しずつ、材料表面や界面の問題になっていったのです。 本章では、私の行なったこのような研究について説明します。 6.1 アルミニウムとシリコン基板の界面状態の評価(1)-(4) これまで、半導体素子の特性に直接関係した部分より、むしろ、外部端子との接続とか、配線の腐食のような、素子特性には直接関係しないけれど、半導体素子の不良率の低下にもっとも寄与するような要因の検討についての研究を紹介してきました。 ここでは、いよいよ、半導体素子の使命である素子特性の改善に関する結果を紹介しましょう。といっても、私が自分の意志で始めた問題ではなく、工場から不良の相談を受けたことから始まりました。 素子特性のことなど知らない私ですが、相談されたので、気軽に話を聞き、検討に入りました。自分のやらなければならない仕事ではないので、いくらか遊び半分で調べ始めました。 ショットキー・バリア・ダイオード(Schottky Barrier Diode)という半導体素子は、シリコン(Si)に、アルミニウム(Al)のような金属を接触させて作ります。接触は蒸着(真空中でAlを蒸発させてSi表面上に堆積させる)によって作ります。 この素子では、電流の方向によって、流れ易さが変わります。この特性は、Al/Si界面状態の影響を大きく受けます。そして、この界面状態を決めるのは、主として、蒸着前のSiの表面処理と、Alの蒸着の仕方です。 ここでは、Al蒸着法の違いが素子特性に与える影響について説明します。 蒸着前処理として、ふっ酸(HF)でSi表面の酸化膜を化学的に除去してから、Al蒸着を行ないます。この蒸着を、従来の電子線蒸着からスパッター法に変えたら、素子特性が変わってしまったという問題の検討についてこれから説明します。 ここで、電子線蒸着というのは、Alの塊(実際には板)に電子線を照射すると、Alが熱せられ、蒸発することを利用します。一方、スパッター法というのは、真空中に少量のアルゴンガスを導入し、電圧をかけると放電して、発生するアルゴンイオン(正の電荷を持つ)が蒸発源(陰極)のAlにぶつかると、Alがガス状になって表面から飛び出し、それが基板(Si)に堆積されます。 問題の素子特性は「順方向電圧」といって、電流の流れやすい方向の電圧をかけたときに、素子(ダイオード)面積100平方μm(ミクロン)当たりの電流が10μA(マイクロアンペア=百万分の一アンペア)になるときの電圧の値です。 蒸着法を変えると、この値が大きくなってしまった(この値を一定の値にしたい)ので、私達はエスカを使って、その原因を調べました。 そのためにはAl/Si界面を調べる必要があると考えました。しかし、この前に測定したSiO2/Si構造の試料とは違って、厚い(1μmぐらい)AlがSiの上にあるのです。つまり、このままでは、エスカによる界面分析は無理です。 エスカで分析できるのは深さ10nm程度です(1nmは1μmの千分の1)。 このような場合、通常は「イオンエッチング法」が使われます。エスカ装置内でアルゴンイオンを試料表面に当てて、少しずつ削っていく(薄くしていく)のです。 ここで、「エッチング」というのは、腐食させて(溶かして)材料を掘っていくことです。銅板などの版画を作るのには、酸で掘りたい部分を溶かしていきます。 このイオンエッチングはどの材料にも使えますが、薄くするのに、しばしば長時間かかり、装置内を汚したりもします。また、残したいと思う材料も削ってしまうことがありますし、材料の状態を変えてしまうこともあります。 例えば、SiO2がSiO1.9になってしまったりするのです。さらに、材料内部にあるSiO2がなくなってしまったり、その厚さが分からなくなってしまう可能性もあります。 本研究では、新しい(本当は古い;表面(界面)分析でほとんど使われなかっただけ)試みとして、水溶液中で上のAlを溶かしてしまい、Al/Si界面が露出したところをエスカで調べるという方法を使いました。 この方法は、試料を水溶液(エッチング液)に漬けたり、洗浄や乾燥したりするので、真空中の分析ということから考えると、汚らしい方法であると思われるかもしれませんが、液を選ぶことにより、下の材料を溶かさないようにすることができます。また、汚染があったとしても、違う試料の結果との差を見ること(相対的な評価)はできる場合が多いのです。 今回は、エッチング液にリン酸(H3PO4)を使いました。この液は、Alは溶かしますが、SiO2もSiも溶かしません。 結果を表6.1に示します。 表6.1 素子特性とエスカで測ったAl/Si界面のSiの酸化度との関係  Al膜を電子線蒸着法とスパッタ法で作った場合の素子特性(順方向電圧)とAl/Si界面のSi酸化度の関係が示してあります。 素子特性に関しては、スパッタ法でAlを蒸着すると、順方向電圧が高くなりました。 それに対して、エスカの測定では、表6.1と図6.1に示すように、スパッタ法の場合、より厚いSi酸化膜が形成されていることが分かりました。即ち、O(酸素)のピーク強度も、Siピークの酸化したSiの強度も高くなっていました。  図6.1 二つの蒸着法で作ったAl/Si界面でのSiの酸化状態の比較 表6.1には、OとSi(酸化していない)のピーク強度(高さ)比(O)/(Si)(Si酸化度)と、その比から求めた酸化膜厚(エリプソメーター膜厚に相当)が示してあります。結果として、 1.スパッタ法の場合の方が順方向電圧が高くなるのに対応して、酸化膜厚が0.20nm厚くなっていた。 2.蒸着前の表面処理のみの場合と比べると、Al蒸着ありの場合の方が酸化膜厚が大きくなっていた。 ということが分りました。 表6.1に示したように、順方向電圧と(O)/(Si)との相関が得られたのはもっともなことです。スパッタ法でAlを蒸着した場合に、Al/Si界面に形成されるSi酸化膜(電気が流れにくい)が電子線蒸着の場合より厚くなったため、同じ電流を流すために、より高い電圧をかけなければならないと考えられるからです。 しかし、ここで、一つ「疑い」が出てきます。 「なぜ、Alを蒸着することでSiの酸化が進んでしまうのでしょうか?」 この蒸発源のAlにはそんなにO(酸素)が入っていませんし、入っていたとしても、Oは、SiよりAlと結合し易いのです。ですから、 3 SiO2 + 4 Al → 2 Al2O3 + 3 Si のような反応が起きる傾向があります。つまり、Siの酸化が進むのではなく、むしろ、逆に、Si酸化膜が還元される(Si酸化膜が分解してSiになる;薄くなる)傾向が認められるはずなのです。 Siの酸化が進む原因は、次のように考えられます。即ち、Alを蒸着するとき、Siに最初に付着するAlが、金属Alでも、安定なAl2O3でもなく、より不安定なAl(OH)3(Alの水酸化物;酸化物に水の分子がくっついているとも考えられる)のようなものであれば、 4 Al(OH)3 + 3 Si → 3 SiO2 + 2 Al2O3 のような反応で、Siが酸化する可能性があるのです。そして、スパッタで、この不安定なAl化合物の量が多ければ、Si酸化膜が厚くなることを説明できます。 実際に、蒸着のいろいろな段階で試料を取り出してエスカで測定する実験を行なった結果、これが実証されました。 この研究は工場の問題(不良)の解決のために行なったもので、蒸着装置は、研究所から歩いて20分ぐらいの工場にあって、エスカは研究所にありました。ですから、私が指定した、できたての、いろいろな種類の試料を工場の人が自転車で運んでくれたのでした。 そのおかげで、蒸着装置から取り出してから約15分以内に、試料をエスカに入れることができました。 一番驚いたのは、シャッタがまだ閉まっているのに、かなりのAlが、それも「酸化した」(Oが沢山付いた)AlがSi表面で検出されたことです。 シャッタというのは、初期に蒸発させた、汚染の可能性のあるAlが基板のSiに付着するのを防ぐためのものです(カメラのシャッタが光を遮るように)。 スパッタ法でない蒸着では、真空中なので、蒸発粒子はほぼ直線で基板(Si)に到達するのですが、スパッタ法では、アルゴン(Ar)ガスを入れるので、蒸発粒子(Al)がArに衝突する可能性があります。そうすると、進む方向が変わることができます。つまり、シャッタの漏れ(回り込み)があり得るのです(実際にあったのです)。 さらに、このようなAlの量(シャッタが開いているときよりはるかに少ない)は少ないので、装置内に微量でも存在している水や酸素とくっつく可能性が高くなります。(シャッタが開いて、大量のAlが基板に向かって飛んでいるときには、水や酸素が付着したAlの割合はとても小さくなります。) これで原因も分かって、対策として、蒸着後加熱をしてやると、上記のSi酸化物とAl金属の反応が実際に起きて、Si酸化膜を薄くできました。 <まとめ> 半導体工場の問題解決の過程で、 「Al」がSiを酸化させてしまう という、面白い現象に出会うことができ、エスカを駆使して、その実態を明らかにしました。 また、「まんずやってみれ!」で、いろいろ試した結果、Al/Si界面状態の分析手法も考え出すことができました。 この分析法は、既に界面ができている場合には、上の材料を化学的に溶解し(エッチング)、除去するというものです。溶液を選ぶことにより、界面そのものの露出が可能となります。 また、界面を作りながらエスカ分析を行なうという方法も考えました。下の材料(Si)の表面処理後から、蒸着装置に入れ、シャッタを開ける前、開けた直後、Alを少しずつ厚くしていくなどの過程で、試料を装置から出しては、エスカ分析を行ないました。 エスカ分析の結果、この問題においても、Si酸化膜厚を「チェック機能」として使えることが分かりました。この厚さの大小と素子特性(順方向電圧)の変動とを対応付けられました。また、上記の界面分析により、変動を起こす原因も突き止めることができました。 7000字 10/04/22 6.2 モリブデン(Mo)とシリコン(Si)の界面状態の評価(5) 本節では、パソコンとか携帯電話などに使われる記憶素子(いろいろな情報を溜めておく素子)の開発での問題解決例を示します。特に記憶容量の大きい素子(超高集積記憶素子)開発の初期の段階の研究です。 会社もこの分野に力を入れ始めていましたし、私の方もエスカがだんだん使えるようになり、いろいろな問題解決に必要な「大事な証拠(事実)」を得ることができるようになってきました。 私の研究も、これまでは従来技術の改良の研究でしたが、少しずつ、最先端の超高集積回路(ULSI:Ultra-large Scale Integration)に関係した仕事が増えてきました。その当時は、ちょうど1メガビット(Mb)の記憶容量の素子(DRAM: Dynamic Random Access Memory)の開発が始まる少し前でした。(この素子では、数平方cmの面積の中にこれだけの情報を記憶しておけるのです。) ここで、「メガ」というのは百万のことです。ビット(bit)というのは0か1の情報(二進法の)のことです。1980年代にこの素子の開発が始まり、今はギガ(十億)ビットの時代になっているようです。 つまり、当時は、個々の素子等の大きさが1ミクロン程度だったのが、今はその十分の一以下になっているのです。 この微細化によって、素子に接続する電極・配線に使う材料に大きな負担がかかるようになります。即ち、電気抵抗が高くなってしまうのです。そうすると、素子の温度が上がるし、消費電力も高くなります。 ということは、従来より、電気を通しやすい材料を使う必要があるということです。 長さL、断面積Aの配線の電気抵抗Rは R = ρL/A と表せます。ここで、ρ(ロー)は比抵抗で、物質の電気の通りにくさを表す数です。 高集積化で、Lが長くなったり、Aが小さくなれば、当然、抵抗Rは高くなってしまいます。 電極・配線材料には、素子の内部(下部)では、従来は、多結晶シリコン(polySiと書き、沢山の結晶からなるSi;素子の基板に使うSiは単結晶です;polyは polycrystallineの略)を使っていました。(半導体素子の外側(上部)のリード線とつなぐところではAlを使っています。) なお、polySiのρは1mΩ・cm程度、Siと金属の化合物(シリサイド)のそれは数10μΩ・cmで、金属だと数μΩ・cmです。(ここで、mは千分の1、μは百万分の1のことです。) このような事情から、当時、polySiに代わる電極・配線材料として、シリサイドや金属を使えるようにしようとする研究が盛んになったのでした。 わが社の研究所(他の研究室と工場との共同研究)でも、記憶素子用の電極として、比抵抗ρの低い材料の使用を検討を始めました。 そのために、Mo/polySi(ニ層)構造の電極を考えました。SiO2に接触する材料は従来と同じpolySiで、上にあるMoのおかげで電気抵抗が低くなるという都合の良いものでした(もしできれば)。そして、研究所(私ではない)では、なんとかできそうだという感触を得て、工場と一緒になって本格的に検討を始めました。 ところが、大きな問題が発生してしまいました。 調べて分かったことは、 1)polySi上にMoを蒸着した(スパッタ法)だけの段階ではMo/polySi間の電流は流れ易い。 2)しかし、素子形成プロセス中に1000℃で窒素(N2)中1時間の加熱により、電気抵抗が100平方μm当たり1万から100万Ωにもなってしまう。 ということです。 これでは、電極として使えません。そして、私に声がかかったのです。 このことがきっかけで、私が半導体素子そのもの(電気特性を作り出すところ)の研究に、それから少しずつ関わっていくようになってしまったのでした。 上記の不良の症状を聞いて、私にはピンときたのでした。つまり、Mo/Si界面にSiO2(比抵抗が大きい)ができて配線の抵抗が高くなるのではないかと考えました。 前回のAl/Si界面の研究からの連想です。、そのときはSiO2が若干厚くなっただけでしたが、今回は、もっとはっきりした結果です。材料(MoとpolySi)の性質からも、そのようなことが起こる可能性が十分考えられました。 即ち、Mo蒸着の初期の段階に、O(酸素)がMoに含まれていれば、Siの酸化は十分考えられるということです。 2 MoOx + x Si → x SiO2 + 2 Mo のような反応でSiO2ができます。 これは、Alの場合とは違い、起こって当然の現象です。つまり、Siの酸化物はMoのそれより安定(SiとOの方がMoとOより結合し易い、結合が強い)なので、加熱すれば、当然、上式で、反応は左から右へ進むはずです(Moが酸化していても、OをSiが奪い取る)。 この予想の確認をまず行ないました。 そのために、Moを150 nm polySi上に蒸着して(nmとは10億分の1メートル)、これを1000℃のN2(酸素を1-3 ppm(百万分の1の割合) 含む窒素)中で1時間加熱しました。そして、リン酸系のエッチング液で上のMoを除去しました。 そのとき面白かったのは、加熱した試料をそのままエッチング液に漬けてもMoは溶けませんでした。表面をエスカで調べると、Moの他に酸化したSiが検出されました。 このことから、表面がSi酸化膜で覆われているのではないかと考え、SiO2を溶かせるふっ酸(HF)に試料を漬けてから、Moエッチング液に漬けると、Moは容易に除去できました。なお、加熱する前の表面にはSi酸化膜はありませんでした。 Moを除去して、加熱前後のpolySi表面をエスカで調べると、 加熱前では、厚さ1.6 nm のSi酸化膜が、 加熱後では、厚くなって厚さ8.0 nm になっていました。 なお、Moを蒸着する前のSi表面のSi酸化膜の厚さは0.6nm程度でした。 これで分かったのは、 まず、Moを蒸着しただけでpolySiが若干酸化していること、 それから、加熱すると相当酸化が進む ことです。 このO(酸素)はどこから来るものでしょうか。 1) 加熱雰囲気中の酸素が界面まで入っていったのか、 2) 蒸着するMo中に酸素か水が含まれていたのか、 の二つの可能性が考えられます。 最初の可能性、加熱雰囲気の影響を調べるために、Siを高真空中(10^-5 Pa:10の-5乗パスカルの圧力)でも、N2中(不純物として酸素を含む)でも加熱してみましたが、Si酸化膜厚は変わりませんでした。 この結果から、酸素は、蒸着したMoに含まれていたと考えられました。 そこで、その確認のために、polySi上にMoを蒸着していく(界面形成)過程をエスカで「観察」しました。 計10000字 09/4/23 それには、Mo蒸着工程のいろいろな段階で、試料を抜き取って、試料をエスカで測定しました。 測定は、同じ試料を、工程を追って測定していったのではありません。それをやると、実際の試料と比べ、空気に触れる時間が長くなってしまったり、蒸着装置(真空)から試料を取り出すときに空気に触れて酸化が進んでしまったり、吸着物が増えてしまったりするからです。 毎回、新しい試料を、決まったやり方で、ある段階まで進めたものを抜き取って、エスカで測定しました。(それぞれ、工場で試料を抜き取ってから15分以内に測定開始) これらの実験の結果を、図6.2(polySi表面)と図6.3(Mo表面)を使って説明します。  図6.2 Mo蒸着と加熱に伴うpolySi表面状態の変化 まず、図6.2の下の二つのスペクトルで示す、polySiの前処理(ふっ酸)から蒸着装置内での加熱(350℃)の段階では、酸化状態の変化はほとんどありません。 次に、Mo蒸着(スパッタ法)の準備として、シャッタを閉めたままで、予備スパッタを行ないます(初期汚染を除き、一定速度で蒸着できるようにするため)。 この段階では、MoはpolySi上には蒸着されていないはずなのですが、図6.3の一番下のスペクトル(SEV. nm: Moの厚さが数nmということ)に示すように、Alの場合と同じで(前節)、MoがpolySi表面上で検出されました。 そして、シャッタを開けて直ぐ(10 nm 厚)がその上のスペクトルで、一番上が150 nm 厚のものです。 これらのスペクトルで、一番下のものが上二つと明らかに違っています。Moのスペクトルは二つのピークからなっています。酸化すると二つのピークが一緒に低運動エネルギー側に動きます。 一番下のスペクトルは、酸化して二つのピークが動いて、酸化したMoの高エネルギー側のピークが、酸化していない金属Moピークの低エネルギー側のピークと重なっている状態を示しています。ここで、高エネルギー側の二つのピークの比MはMoの酸化状態の目安となります。全く酸化されてないと考えられる状態で 0.64 ですので、150 nm 厚ではほんのちょっと酸化しているということになります。 つまり、界面から 10 nm 程度までの領域ではMoがかなり酸化していました。そして、この段階で(蒸着しただけで)、polySiがある程度( 1.6 nm )既に酸化していました。 Moの厚さを 150 nm にしても、Si酸化膜の厚さは変わりませんが、1000℃で加熱すると、8.3 nm にまで酸化が進みました。  図6.3 Mo蒸着に伴うMo表面状態の変化 そして、1000℃、N2中加熱時に、酸化したMoと下のpolySiとの反応がさらに進んで、Si酸化膜厚が 1.6 nm から 8.3 nm まで増えるのです。 一方、Moの方は、図6.4に示すように、酸化していたMoが、Si存在下で加熱される(1000℃、N2中)と、酸化Moが還元されて(元の状態に戻る)、金属Moになります(一番下とその上のスペクトル)。 但し、同じ雰囲気中でもSiがないと、雰囲気中の1-3ppmの不純物酸素によって酸化されてしまいます(一番上)。  図6.4 加熱中のSiの存在と雰囲気がMoに与える影響 まとめると、polySiは、蒸着初期(シャッタが開く前)にpolySi上に堆積される酸化したMoの酸素によって酸化されるということが分かりました。 <どうしたらよいか?> Mo/polySi界面でのpolySiの酸化を抑えるにはどうしたらいいのでしょうか。 一つには、Mo中の酸素を減らすことですが、そうすると、今度は、他の反応が起きる、つまり、MoとpolySiが反応し易くなります。 Mo + 2 Si → MoSi2 Moより高抵抗になるのが許されるなら、これでもいいのですが、この反応が起きると、MoSi2形成時に体積収縮(>20%;縮む)があり、剥がれやすくなります。 また、酸素の量を制御して、酸化膜厚を2 nm 以下に制御できればいいのですが(この状態を当初研究所で偶々作ってしまったと思われます)、再現性に問題があります。 もう一つは、Mo中に酸素があっても、下のpolySiと反応しなければいいのです。しかし、この場合も、MoとpolySiの反応は避けたいです。ですから、前もって、MoにSiを加えておけばいいのです。そして、安定性を考えると、MoSi2にするのがいいのです。 以上のことを考えて、結局、MoSi2構造の電極にすることにより、今回の問題は解決して、1 Mb(メガビット)の一つ前の段階の記憶容量の記憶素子に使われました。 この研究は、半導体関係の問題解決のためにエスカがとても役に立つということを示したものでした。 そして、私の問題解決の考え方の一部としても、エスカの「チェック機能」としての威力を発揮することができました。 即ち、Mo/Si界面のエスカ分析により、電極形成プロセスの良し悪しの判定だけでなく、悪いときの原因を明らかにするための証拠を得ることもできました。事実により、どのような対策が可能かを確実に示せたのです。 一方、半導体プロセスでの各種問題において、酸素が関係していることが多いことも分かってきました。 今回、最初に、研究所で「うまく行った」と思ったのは、酸素のお陰でした (Mo/極薄SiO2/polySiができていた)。そして、工場へ行って、「うまく行かなかった」のも、酸素のお陰(制御できなかった;SiO2が厚くなってしまった) でした。そして、最終的な答えも、酸素の制御をうまく行なえるようにした(MoSi2にしてしまう)ことでした。 このように、良きにつけ、悪しきにつけ、酸素が絡んでいることが多いのです。 実際に、前節、Al/Si界面の問題では、酸素の影響を全部なくせたとすると、あの素子(ショットキ・バリア・ダイオード)はできなくなってしまいます。界面でAlとSiが反応して、素子にはならなくなってしまいます。 これは笑い話なのですが、当時、アメリカの、もっと良い蒸着装置を持っていた、ある会社では、SiとAlの間に反応を防ぐ層を挟んで、この素子を作っていました。ところが、私のいた会社では、偶々、界面のSiが酸化したお陰で、この反応防止層なしで、うまく行っていたのでした。 この会社の研究者が来たときに、この話になって、先方は私達の話を聞き、びっくりしていました。ちょうど私がなぜかを調べた後だったので、私は、少し得意になって、酸素の制御ができることを「自慢」したのでした。 実際に、これだけ同じように蒸着できるようにした工場の技術者の力は大したものであると思いました。(ですから、最初から工場でやっていたら、「Mo/polySi」構造の電極もできてしまったかもしれません。) 次節では、最先端プロセス技術への挑戦(次章:第7章)への最後の準備となる研究結果について説明します。 計13300字 6.3 SiO2/SiO2同士の界面の分析(6) ここでは、Si酸化膜の上にSi酸化膜を重ねた構造で、密着性が悪く(剥がれやすく)なる場合の解析例を紹介します。 ここで用いた方法は、密着性の良い場合と悪い場合について、Si酸化膜を重ねる前の表面状態を比較するというやり方です。これまでのやり方では違いをはっきりさせられなかったのに、今回使った新しい手法で、界面を作る前の表面状態の微妙な差が密着性低下の原因となっていることを突き止めました。 これまで、表面(界面)の化合状態を調べるには、エスカで測定したピークの位置あるいは強度にしか着目していませんでした。しかし、今回のような微妙な違いの場合、ピークの形の変化にも気づかなければいけないということが分かりました。 エスカはその当時かなり知られてはいましたが、実際に使うときには、普通のやり方だけではなく、臨機応変に、自分でいろいろな新しいことをやってみる必要があると感じました。 「まんずやってみれ!」です。 考えてみると、エスカというのは、本当の意味の微量分析は得意でないのです。微量の不純物を検出したくても、せいぜい0.1%程度です。 特に、電気特性に関係した不純物や欠陥は、とても微量でも(0.1%よりはるかに少なくても)問題になる可能性が高いのです。 今回の例でも、シリコンの酸化状態が関係していることが分かりました。このように、私のところに来る多くの問題には酸化が絡んでいることのが多かったのです。問題を具体的に説明しましょう。 半導体素子の形成では、素子表面に配線となるアルミニウムを全面にまず蒸着してから、不要な部分をエッチングで取り除いてしまいます。(アルミニウムの蒸着直前の段階では、表面はほぼ全部シリコンの酸化膜で、一部にシリコンが露出しているという状態です。) この不要なアルミニウムを除去した後に、保護膜にシリコン酸化膜をまた蒸着します。 ここで今回の問題が発生しました。普通、シリコンの酸化膜の上にシリコンの酸化膜を蒸着しても何も問題はないのですが、一度、アルミニウムを蒸着し、それを除去した状態というのが問題だったのです。このときに、シリコン酸化膜同士の密着性が悪くなってしまったのです。 この研究の目的はこの原因を突き止めることでした。 私達は、まず、上記事実を再現実験で確認しました。 上記の不良が確認できたので、エスカを使って、シリコン酸化膜表面に与える、アルミニウム蒸着の影響を調べました。 まず、一度アルミニウムを蒸着してそれを除去した場合と、アルミニウムを蒸着しない、即ち、シリコン酸化膜蒸着のままの場合との比較を行ないました。 従来のやり方では、測定したSi2p、O1sとC1s(有機吸着物の炭素)のピークの位置、相対強度(ピーク高さの比)と半値幅について、上記の二つの場合の違いを認められませんでした。ここで、半値幅とは、ピークの半分の高さでのピークの幅のことです。 しかし、両者の間に密着性の違いがあるのは確かなので、私達は上記のエスカの結果に不満でした。そこで諦めないで、詳細に結果を見直すと、新しいことが分かりました。 それが、図6.5の上の二つの測定結果です。  図6.5 表面状態の変化に対応したピーク形状の変化 最初は目視で感じたことです。つまり、ピークの対称性が、アルミニウム蒸着の有無で違っていると思われました。即ち、アルミニウム蒸着有の場合の方が、高運動エネルギー側へ裾を引いている(ピークの高運動エネルギー側が膨らんでいる)ように、私には見えたのです。 ピークの半分の高さでは有意差が出なかったので、1/4の高さのところで、高運動エネルギー側の幅W+と低エネルギー側のそれW-との比R(対称性とでも呼びましょう) R=W+/W- に着目しました(図6.5では、W-の添え字(-)がよく見えません)。 ピークの形の違いを対称性Rによって比べてみると、自分で感じたように、アルミニウムを蒸着する(基板温度250℃で行なっています)ことにより、ピークの高運動エネルギー側に膨らみが出てくることが分かりました。 この結果は、6.1節で論じた、シリコン酸化物とアルミニウム酸化物との安定性の違いからも、うなずけるものです。即ち、 3 SiO2 + 4 Al → 2 Al2O3 + 3 Si という左から右へ進む反応(SiO2の還元反応)が起き易いからです。 もし、この反応によってSiO2が還元されると、反応によって生成する、酸化していないシリコンは、より高運動エネルギー側に現われるはずです。 しかし、実際には、その前に、シリコンと結合している酸素の数が4個(SiO2の場合)より少ない、還元の途中段階の状態がまず現われるのではないかと考えられます。 そうすると、それらの状態に対応するピークは、初めは、孤立したシリコンのピークより、むしろ、SiO2のピークの高運動エネルギー側の膨らみとして現われるのではないかと考えられます。 第4章で論じた、SiO2とシリコン基板との界面にあるような化合状態のシリコンに対応するのではないかと考えます。 この辺の事情ももっと理解するために、積極的にアルミニウムとシリコン酸化膜の反応を促進させ、どうなるかを調べました。そのために、より高温の480℃で加熱を行ないました。 その結果が、図6.5の下の2つのスペクトルです。予想を支持する結果が得られています。 まず、この加熱により、ピークの対称性R(この値が1のときピークは対称)の値が、時間とともに、1.11、1.19と大きくなっています。さらに、一番下のスペクトル(加熱時間6時間)では酸化していないピークであると思われるものがはっきりと認められています。 以上の結果により、アルミニウムをシリコン酸化膜の上に蒸着する(基板温度250℃)だけで、シリコン酸化膜がアルミニウムによって還元され始めると結論しました。但し、この段階では、シリコン酸化膜が完全にシリコンに還元されているのではなく、SiO2の不完全な還元状態が生じたと考えられます。 この状態(エスカで判定可能)と密着性低下との対応付けができたということで、この研究の目的は達成されました。(対策としては、変質したSiO2表面層をふっ酸で溶かしてやればいいのです。) しかし、「なぜ密着性が低下するのか」という疑問に対しての答えはまだ分かりません。 16100字 4/26 6.4 まとめ この頃、私は、会社の仕事にかなり慣れてきて、エスカもなんとか使えるようになっていました。そして、上記のような研究のお陰で、会社で研究を続けていけそうな気がしてきました。私はエスカの研究に夢中になっていたのでした。 これらの研究例では、これからの開発研究に必要な手法を考え出すことができて、得られた知見も興味深いものでした。さらに、これらの研究の実行も、楽しく、面白いものでした。 これらは、本来の私の仕事ではありませんでした。全て、工場など他部門からの依頼で行なったものでした。ですから、ある意味では、失敗を恐れずに、気軽に行なうことができました。「遊び心で」思いついたことを何でも試せたと言えるでしょう。これも、研究が面白かった理由の一つになるでしょう。 結果として、試しにやったことが皆「本番」になってしまいました。つまり、何でもありなのです。(なお、ここで白状すると、半導体技術開発の研究も、表面、界面の研究も、工場の不良解析も、ほとんど全部素人として始めたものです。) 「まんずやってみれ!」です。 いろいろなことを自由に試すことが研究をますます面白くしてくれました。このような経験から、本来の技術開発の仕事でも、気軽に、いろいろなことを試せるようになってきました。 「面白かった」ということで、私がこれから会社で研究を続けられそうだと思うようになってきました。 また、半導体技術開発の研究も、かなりの部分は表面(界面)の研究と捉えることができ、さらに、似たような現象が関与しているので、様々な研究を、大きな研究の一部と考えることができそうです。 私の「表面(界面)の研究」は、組成とか、化合状態そのものを求めるだけでは駄目なのです。製造工程の良し悪しとか、使用中の製品の不良率などとの対応付けができるような知見が欲しいのです。 本章を含む、これまでの検討で、このようなことができることが分ってきましたが、これからの研究でまだまだいろいろな問題が発生することが予想できます。 1. 界面測定法のさらなる改善 2. 微量不純物や欠陥の検出(従来の測定限界以下の) などです。 最後に、工場からの相談が、私の研究にとって極めて重要であったことを強調したいです。エスカの使い方をいろいろ考え出せるだけでなく、製造や使用中に問題となるいろいろな現象を洗い出すこともできたのです。勿論、工場の問題解決のお手伝いもできました。 次章では、最先端技術開発への挑戦について説明します。 17200字 10/4/27 6.5 最後にもう一言 本章で示したような、エスカを使った研究を行なうことで、やる気が出てきたのは、やったことが役に立ったばかりでなく、楽しかったからです。 第一には、初めての経験が多かったからです。やることや分かったことが新鮮で、面白いと感じることが多かったのです。それは、半導体の技術開発も、エスカの研究も、ほぼ白紙状態で始めたからではないかと思います。(子供が新しいことを知ろうとするときのように) 第二に、いろいろな問題の解決に、エスカによる評価が役に立ったからです。解決の鍵となる「事実」(証拠)を得ることができたからです。(チェック機能になった。) その結果、半導体製造技術の問題を表面(界面)の研究にしていくことができたからです。 第三に、様々な内容の問題の原因が、材料は違っても、現象としては同じであることがしばしばあることに気づいてきたからです。 このようなことから、会社で、人間関係などで、嫌なことがあっても、エスカを使った研究を行なったり、問題のことを考えることの楽しさのお陰で、会社で働き続けることができたのでした。 それどころか、会社の仕事が全て、「私独自の、エスカによる表面(界面)の研究」の一部になっていったのでした。 一般的には、表面(界面)の研究というと、どちらかというと、高真空装置の中で作った「清浄」表面(界面)の分析に関するものが多く、私の仕事で扱うような、「汚い」(水や空気、その他の汚染に触れた)表面(界面)を調べるものではありませんでした。 このような試料を測定するのが「私の研究」だと位置づけて、自分の研究を、 「実用表面(界面)の研究」 と呼ぶことにしました。 さらに、この研究では、分析技術として、組成とか化合状態そのものを求めることが目的ではなく、むしろ、問題となる特性(不良率など)と対応のある指標(なんでもいい;ピーク強度比とか)を見出し、利用することに自分の力を集中させました。 これがまた私の研究に自由度を与えてくれ、研究を面白いものにしてくれました。学問的ではないかもしれませんが。 18000字 10/04/28 参考文献 1) 岩田誠一、山本博司、菊地彰、中田健介:「Al/Si界面状態とショットキ・バリア・ダイオード特性との関係」、日本金属学会誌、45(1981), 542-543. 2) A. KIkuchi, H. Yamamoto, S. Iwata and T. Ikeda: "Electron transport across aluminum/ultrathin silicon oxide/phosphorus implanted silicon barriers," J. Appl. Phys., 51(1980), 4913-4918. 3) A. Kikuchi and S. Iwata:"Effect of Sputter Etching on Aluminum-Silicon Schottky Barrier Diode Characteristics," Jap. J. Appl. Phys., 22(1983), L577-L579. 4) 岩田誠一、中田健介、菊地彰:「アルミニウム蒸着時のシリコン基板の酸化」、日本金属学会誌、50(1986), 287-292. 5) 岩田誠一、山本直樹、小林伸好:「Mo/Si界面でのSi酸化膜の形成」、日本金属学会誌、51(1987), 138-141. http://www.jim.or.jp/journal/j/pdf3/51/02/138.pdf 6)岩田誠一、石坂彰利:「ESCAによるAl/SiO2反応の検討」、日本金属学会誌、45(1981), 544-545. ジャンル別一覧

人気のクチコミテーマ

|

||